# Serial ATA International Organization

Version 1.00RC 12-July 2007

# Serial ATA Interoperability Program Revision 1.2 Agilent MOI for SATA RSG Tests

This document is provided "AS IS" and without any warranty of any kind, including, without limitation, any express or implied warranty of non-infringement, merchantability or fitness for a particular purpose. In no event shall SATA-IO or any member of SATA-IO be liable for any direct, indirect, special, exemplary, punitive, or consequential damages, including, without limitation, lost profits, even if advised of the possibility of such damages.

This material is provided for reference only. The Serial ATA International Organization does not endorse the vendor equipment outlined in this document.

# TABLE OF CONTENTS

| TABLE OF CONTENTS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 2   |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| MODIFICATION RECORD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 3   |

| ACKNOWLEDGMENTS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 4   |

| INTRODUCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | S   |

| GROUP 1: RSG REQUIREMENTS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 6   |

| TEST RSG-01: GEN1 (1.5Gb/s) RECEIVER JITTER TOLERANCE TEST                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |     |

| TEST RSG-02: GEN2 (3.0Gb/s) RECEIVER JITTER TOLERANCE TEST                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |     |

| APPENDICES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 9   |

| APPENDIX A – GENERAL RESOURCE REQUIREMENTS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |     |

| APPENDIX B – SSG CALIBRATION PROCEDURE (USING AGILENT DSO81204 REAL-TIME DSO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |     |

| AS THE JMD)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 13  |

| APPENDIX C – SSG CALIBRATION PROCEDURE (USING AGILENT N4903A J-BERT AS THE JM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | ID) |

| (Informative)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |     |

| APPENDIX D – SSG CALIBRATION PROCEDURE (USING AGILENT 86100C DCA-J AS THE JMI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |     |

| (Informative)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |     |

| $Appendix\ E-Using\ the\ Agilent\ N4903A\ J-BERT\ as\ the\ Stressed\ Signal\ Generator$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |     |

| (SSG) (Informative)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |     |

| $Appendix \ F-Using \ the \ Agilent \ 81133/4A \ Pulse/Pattern \ Generator \ as \ the \ Stresseight \ Stresseight$ |     |

| SIGNAL GENERATOR (SSG)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 27  |

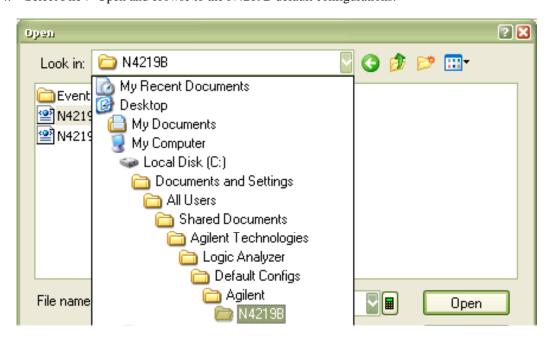

| Appendix $G$ – Using the Agilent N4219B Serial ATA Probe as the Frame Error                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |     |

| DETECTOR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |     |

| APPENDIX H – USING THE CRESCENT HEART SOFTWARE SATA-II PROBE AS THE FRAME ERR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |     |

| DETECTOR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |     |

| APPENDIX I – SUGGESTED INITIAL AMPLITUDE AND DJ/RJ SETTINGS FOR VARIOUS SSG SET                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |

| (INFORMATIVE)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |     |

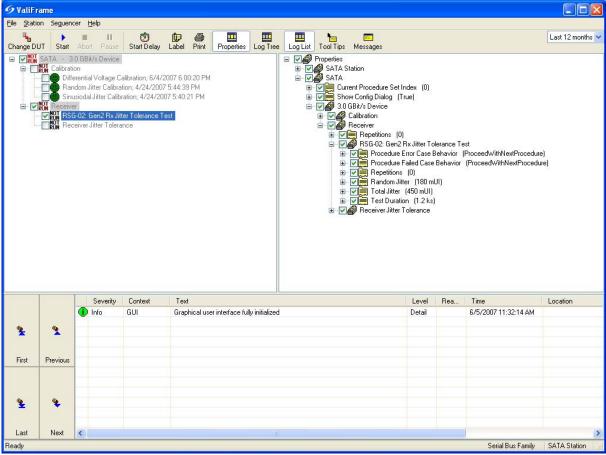

| $Appendix \ J-Using \ the \ Agilent \ N5990A \ Test \ Automation \ Software \ Option \ 103$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 39  |

# MODIFICATION RECORD

# 2007 Jul 12 (Version 1.00RC1) Editorial update following 12Jul 2007 RC approval

Andy Baldman (UNH-IOL): Cover Page: Updated document version number to 1.00RC.

### 2007 Jun 07 (Version 0.92) ADDITIONAL UPDATES, POST-IW3

Andy Baldman (UNH-IOL): Acknowledgements page: Added Hermann Stehling, for Bitifeye contributions of automation software.

RSG-01 and RSG-02: Added note at bottom of procedure to cover premature test abortion for cases when

excessive errors are observed (i.e., >1000) for any test case, as per the UTD.

Appendix A: Added Agilent SMA cables and part numbers to equipment list.

Appendix A: Added model numbers of suitable equivalent Noisecom sources to equipment list.

Appendix A: Added E4432B sine source to equipment list as suitable DJ source.

Appendix I: Added initial starting settings for using E4432B as DJ source with 81134A SSG.

Added new Appendix (Appendix J), for Bitifeye automation software.

# 2007 Apr 28 (Version 0.90) MINOR UPDATES IN RESPONSE TO 17APR2007 REVIEW.

Andy Baldman (UNH-IOL): Cover Page: Updated SATA logo to trademarked version, and added CHS Frame Error Detector.

Entire Document: Changed Noisecom noise source model name from UFX-7110 to PNG-7110.

Appendix A: Changed amplitude procedure BACK to using LBP lone 0/1, rather than ALIGN minimum

amplitude bits.

Renamed Appendix H to Appendix I.

Added new Appendix H for Crescent Heart Software Frame Error Detector.

### 2007 Apr 16 (Version 0.88) Additional major updates

Andy Baldman (UNH-IOL): Entire Document: Updated all DJ references to .270UI, from .320UI.

Entire Document: Removed all references to using 14dB splitters. (50/50 splitters are preferred, for

better return loss and matching.)

Appendix A: Changed amplitude procedure to use ALIGN Minimum Amplitude Bit instead of LBP lone bit.

Appendix D: Cleaned up many typos, and moved J-BERT-specific SSG info into Appendix E.

# $2007\;Apr\;08\;(Version\;0.87)\;$ major update for revision 1.2 interop program

Andy Baldman (UNH-IOL): Entire document: Updated all UTD and MOI references to reflect Program Revision 1.2

RSG-01/02: Changed DJ frequencies from 5/10/62MHz to 10/33/62MHz per UTD updates. Appendix A: Added 14dB pickoff tees to Table A-1, and changed Figure A-3 to a block diagram.

Appendix B: Completely overhauled, adding procedure for amplitude calibration using isolated Lone 1.

Appendices C, D, E: Made informative.

Appendix F: Major rewrite to include procedure for using Noisecom PNG-7110 noise source.

### (PREVIOUS REVISIONS FOR 1.0 AND 1.1 INTEROP PROGRAMS)

### 2006 Nov 23 (Version 0.85) Additional updates

Michael Herz (Agilent): Added contents on an 81134A-based setup.

# 2006 Nov 22 (Version 0.84) Additional major updates

Andy Baldman (UNH-IOL): Created separate appendices for J-BERT, DCA-J, and real-time DSO calibration.

Created separate appendix for using 81134A-based setup (instead of J-BERT) for jitter generation.

Renumbered all Appendices as a result of above changes.

RSG-01/02: Replaced 'Pattern Generator' with 'SSG', to make more modular, and hardware independent.

### 2006 Nov 13 (Version 0.83) FIRST MAJOR UPDATE

Andy Baldman (UNH-IOL): Updated title page to new revision 1.1 naming conventions.

Added procedures to Appendix B to support multiple Jitter Measurement Devices for calibration purposes.

Added Appendix C for SATA Probe setup and configuration.

# 2006 Sep 24 (Version 0.81) INITIAL DRAFT RELEASE

Andy Baldman (UNH-IOL): Initial Release

# **ACKNOWLEDGMENTS**

The Serial ATA Logo Working Group would like to acknowledge the efforts of the following individuals in the development of this document:

David Woolf Andy Baldman Dr. Michael Herz Hermann Stehling UNH InterOperability Lab UNH InterOperability Lab Agilent Technologies Bitifeye Digital Test Solutions

djwoolf@iol.unh.edu

aab@iol.unh.edu

michael\_herz@agilent.com

hermann.stehling@bitifeye.com

### INTRODUCTION

The tests contained in this document are organized in order to simplify the identification of information related to a test, and to facilitate in the actual testing process. Tests are separated into groups, primarily in order to reduce setup time in the lab environment, however the different groups typically also tend to focus on specific aspects of product functionality.

The test definitions themselves are intended to provide a high-level description of the motivation, resources, procedures, and methodologies specific to each test. Formally, each test description contains the following sections:

### **Purpose**

The purpose is a brief statement outlining what the test attempts to achieve. The test is written at the functional level.

#### References

This section specifies all reference material *external* to the test suite, including the specific subclauses references for the test in question, and any other references that might be helpful in understanding the test methodology and/or test results. External sources are always referenced by a bracketed number (e.g., [1]) when mentioned in the test description. Any other references in the test description that are not indicated in this manner refer to elements within the test suite document itself (e.g., "Appendix 6.A", or "Table 6.1.1-1")

### **Resource Requirements**

The requirements section specifies the test hardware and/or software needed to perform the test. This is generally expressed in terms of minimum requirements, however in some cases specific equipment manufacturer/model information may be provided.

### Last Modification

This specifies the date of the last modification to this test.

### Discussion

The discussion covers the assumptions made in the design or implementation of the test, as well as known limitations. Other items specific to the test are covered here as well.

### **Test Setup**

The setup section describes the initial configuration of the test environment. Small changes in the configuration should not be included here, and are generally covered in the test procedure section (next).

### Procedure

The procedure section of the test description contains the systematic instructions for carrying out the test. It provides a cookbook approach to testing, and may be interspersed with observable results.

### **Observable Results**

This section lists the specific observables that can be examined by the tester in order to verify that the PUT is operating properly. When multiple values for an observable are possible, this section provides a short discussion on how to interpret them. The determination of a pass or fail outcome for a particular test is generally based on the successful (or unsuccessful) detection of a specific observable.

### **Possible Problems**

This section contains a description of known issues with the test procedure, which may affect test results in certain situations. It may also refer the reader to test suite appendices and/or other external sources that may provide more detail regarding these issues.

# **GROUP 1: RSG REQUIREMENTS**

# **Overview:**

This group of tests verifies receiver functionality under stressed-signal conditions, for the purposes of performing SATA-IO Interoperability Testing. These tests are limited to functionality which are covered by tests RSG-01 and RSG-02 (Section 2.15 of the Serial ATA Interoperability Program Unified Test Document Revision 1.2), and do not provide comprehensive coverage of all receiver tolerance requirements defined by the SATA v2.5 spec.

# Test RSG-01: Gen1 (1.5Gb/s) Receiver Jitter Tolerance Test

**Purpose:** To verify that the receiver of the Product Under Test (PUT) can operate without error under stressed signal conditions while operating at 1.5Gb/s.

#### **References:**

- [1] Serial ATA Interoperability Program Revision 1.2 Unified Test Document, Section 2.15.1

- [2] Serial ATA Interoperability Program Revision 1.2 Pre-Test MOI, Appendix B (Framed COMP Pattern)

Resource Requirements: See Appendix A.

**Last Modification:** June 7, 2007

**Discussion:** Reference [1] specifies the basic requirements for Receiver Jitter Tolerance testing for the purposes of the SATA-IO Interoperability Program. These requirements are a subset of the complete set of requirements defined in the SATA standard. Note that this test requirement is only applicable to products running at 1.5Gb/s. For products that support 3.0Gb/s, this test is not required.

**Test Setup:** See Appendix A.

### **Test Procedure:**

Note this test procedure assumes the user has already performed the initial system setup and calibration procedures outlined in Appendices A-H of this document.

- 1) Connect the PUT to the test system as outlined in Appendix A.

- 2) Configure the Stressed Signal Generator (SSG) to send the framed COMP pattern (see [2]) at 1.5Gb/s.

- 3) Turn the output of the generator OFF (i.e., disable all signal output).

- 4) Configure the PUT for BIST-L operation at 1.5Gb/s using the BIST Configuration Tool.

- 5) Turn the output of the SSG ON, but with jitter disabled (i.e., clean, unjittered pattern with nominal SATA amplitude).

- 6) Disconnect the BIST Configuration Tool from the power splitters, and terminate the unused splitter ports with 50-ohm SMA terminators.

- 7) Verify using the Frame Error Detector that the PUT is properly looping back the unstressed framed COMP pattern data without error.

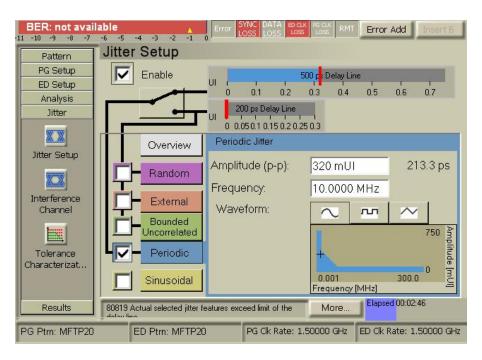

- 8) Configure the SSG for Sinusoidal DJ at a frequency of 10MHz, with the proper DJ, RJ, and Amplitude values determined during the cal procedure for 1.5Gb/s operation. Enable jitter generation on the SSG output, and turn the SSG output ON.

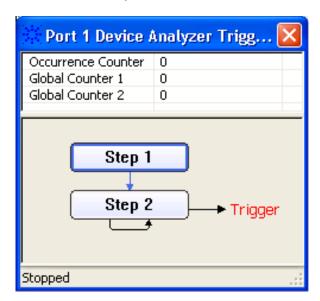

- 9) Reset the counter on the Frame Error Detector.

- 10) Run the test for 20 minutes and record the number of frame errors detected by the Frame Error Detector.

- 11) Repeat steps 8-10 for the 33 and 62<sup>1</sup> MHz sinusoidal jitter frequencies.

Note that for any jitter frequency test case, if 'excessive' errors are observed (i.e., >1000), the test may be prematurely aborted, and a failing result assigned for that test case.

### **Observable Results:**

• For all jitter frequencies, the number of frame errors observed should be zero.

Possible Problems: None

<sup>&</sup>lt;sup>1</sup> If this test is carried out using a J-BERT as SSG, please note that the J-BERT pattern generator is not capable of generating 320mUI sinusoidal Jitter at 33 or 62MHz. At 62MHz a maximum of 121mUI can be generated with RJ turned on and a maximum of 300mUI can be generated with RJ turned off.

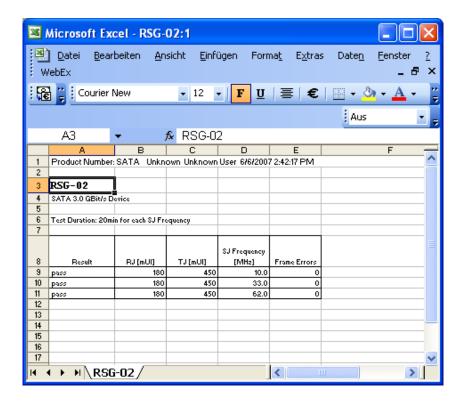

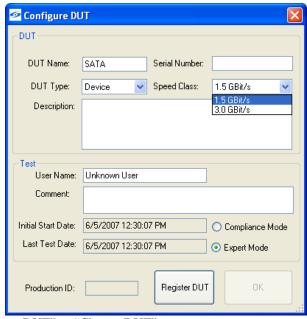

# Test RSG-02: Gen2 (3.0Gb/s) Receiver Jitter Tolerance Test

**Purpose:** To verify that the receiver of the Product Under Test (PUT) can operate without error under stressed signal conditions while operating at 3.0Gb/s.

#### **References:**

- [1] Serial ATA Interoperability Program Revision 1.2 Unified Test Document, Section 2.15.2

- [2] Serial ATA Interoperability Program Revision 1.2 Pre-Test MOI, Appendix B (Framed COMP Pattern)

Resource Requirements: See Appendix A.

**Last Modification:** June 7, 2007

**Discussion:** Reference [1] specifies the basic requirements for Receiver Jitter Tolerance testing for the purposes of the SATA-IO Interoperability Program. These requirements are a subset of the complete set of requirements defined in the SATA standard. Note that this test applies only to products operating at 3.0Gb/s.

**Test Setup:** See Appendix A.

### **Test Procedure:**

Note this test procedure assumes the user has already performed the initial system setup and calibration procedures outlined in Appendices A-H of this document.

- 1) Connect the PUT to the test system as outlined in Appendix A.

- 2) Configure the Stressed Signal Generator (SSG) to send the framed COMP pattern (see [2]) at 3.0Gb/s.

- 3) Turn the output of the generator OFF (i.e., disable all signal output).

- 4) Configure the PUT for BIST-L operation at 3.0Gb/s using the BIST Configuration Tool.

- 5) Turn the output of the SSG ON, but with jitter disabled (i.e., clean, unjittered pattern with nominal SATA amplitude).

- 6) Disconnect the BIST Configuration Tool from the power splitters, and terminate the unused splitter ports with 50-ohm SMA terminators.

- 7) Verify using the Frame Error Detector that the PUT is properly looping back the unstressed framed COMP pattern data without error.

- 8) Configure the SSG for Sinusoidal DJ at a frequency of 10MHz, with the proper DJ, RJ, and Amplitude values determined during the cal procedure for 3.0Gb/s operation. Enable jitter generation on the SSG output, and turn the SSG output ON.

- 9) Reset the counter on the Frame Error Detector.

- 10) Run the test for 20 minutes and record the number of frame errors detected by the Frame Error Detector.

- 11) Repeat steps 8-10 for the 33 and 62 MHz sinusoidal jitter frequencies.

Note that for any jitter frequency test case, if 'excessive' errors are observed (i.e., >1000), the test may be prematurely aborted, and a failing result assigned for that test case.

### **Observable Results:**

• For all jitter frequencies, the number of frame errors observed should be zero.

Possible Problems: None

# **APPENDICES**

# **Overview:**

Test suite appendices are intended to provide additional low-level technical detail pertinent to specific tests contained in this test suite. These appendices often cover topics that are outside of the scope of the standard, and are specific to the methodologies used for performing the measurements in this test suite. Appendix topics may also include discussion regarding a specific interpretation of the standard (for the purposes of this test suite), for cases where a particular specification may appear unclear or otherwise open to multiple interpretations.

Test suite appendices are considered informative supplements, and pertain solely to the test definitions and procedures contained in this test suite.

# Appendix A – General Resource Requirements

**Purpose:** To define the hardware/software requirements for performing the tests defined in this document.

References: None.

Last Modification: June 7, 2007

**Discussion:**

# A.1 - Introduction

In order to perform receiver jitter tolerance testing on SATA transceivers, several pieces of equipment are needed. The primary functional components are as follows:

| Component        | Function                               | Device/Model                                                                               |  |

|------------------|----------------------------------------|--------------------------------------------------------------------------------------------|--|

| Stressed Signal  | Generates jittered/stressed test       | Agilent N4903 J-BERT (Gen2 only)                                                           |  |

| Generator (SSG)  | signal                                 | or,                                                                                        |  |

|                  |                                        | Agilent 81133A (one channel) or 81134A (two                                                |  |

|                  |                                        | channels) Pattern Generator, with either Agilent                                           |  |

|                  |                                        | 33250A or E4432B signal generator (or equivalent),                                         |  |

| Noise Source     | Used as RJ modulation source           | and suitable Noise Source (see list below).  NoiseCom PNG-7110. (Equivalent models include |  |

| Noise Source     | (when using 81134A as SSG.)            | UFX/PNG-7107/08/09/10/12, and                                                              |  |

|                  | (which using 0113+A as 550.)           | NC-6107/08/09/10/12; and                                                                   |  |

| BIST Generator   | Used to enable BIST-L loopback         | PC running Ulink DriveMaster software                                                      |  |

| (BISTGEN)        | mode of PUT                            | <del>U</del>                                                                               |  |

| Jitter           | Used to verify/calibrate SSG           | Agilent Infiniium DSO81304A 13GHz Real-Time                                                |  |

| Measurement      | output                                 | DSO (Recommended)                                                                          |  |

| Device (JMD)     |                                        | (                                                                                          |  |

|                  |                                        | (Agilent 86100C w 54754A, or                                                               |  |

|                  |                                        | Agilent N4903 J-BERT May be used for informative purposes only.)                           |  |

| 3-Way, 50/50     | Used to combine SSG output and         | Agilent 11636B or equivalent                                                               |  |

| Resistive Power  | BISTGEN signal into PUT                | (2 needed for SSG outputs.)                                                                |  |

| Splitter (PS)    | receiver.                              | ( <b>2</b> notata 131 82 8 anpansi)                                                        |  |

| 1                |                                        | (1 additional needed if using 81134A as SSG)                                               |  |

|                  | (Also used to combine sinusoidal       | -                                                                                          |  |

|                  | and random noise modulation            |                                                                                            |  |

|                  | sources into Delay Control input,      |                                                                                            |  |

| Г                | when using 81134A as SSG)              | A '1 (100 100 I ' A 1 ' '1 C                                                               |  |

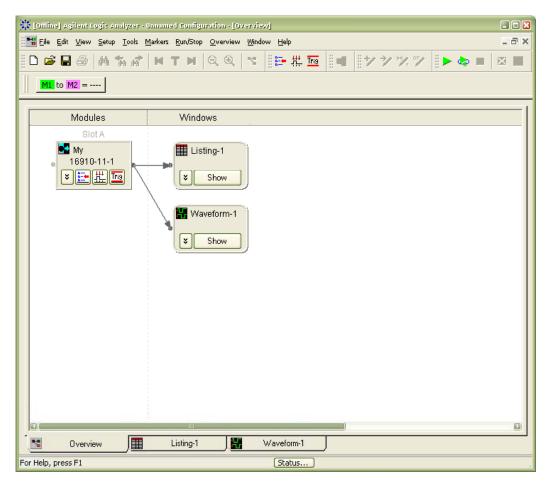

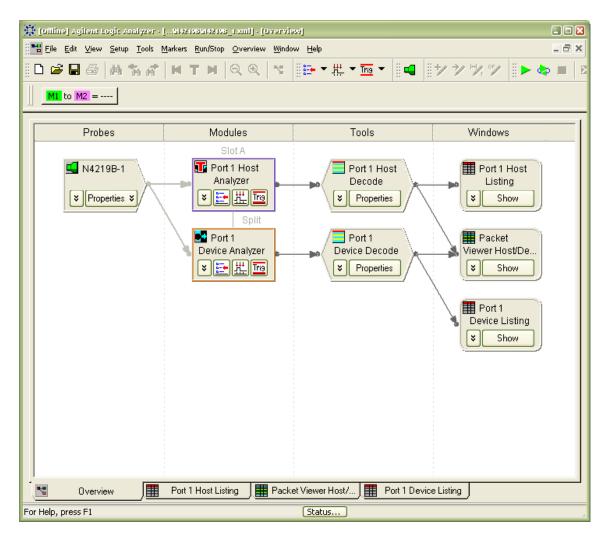

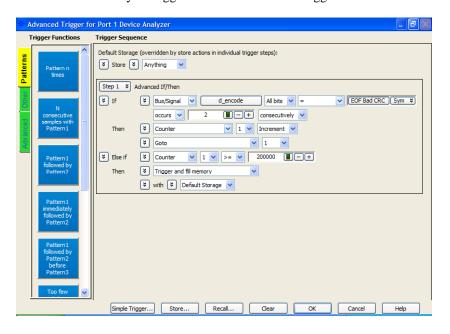

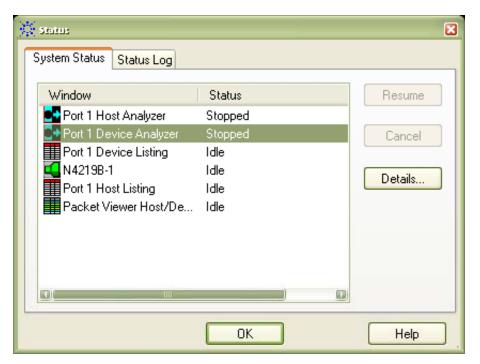

| Frame Error      | Used to monitor frame errors on PUT TX | Agilent 168xx or 169xx Logic Analyzer with one of                                          |  |

| Detector (FED)   | PULIA                                  | the following modules: 16910, 16911, or 16950, and N4219B SATA Probe.                      |  |

|                  |                                        | or,                                                                                        |  |

|                  |                                        | Crescent Heart Software SATA-II Probe                                                      |  |

| Transition Time  | Used to create SSG risetime of         | Agilent N15435A (2 needed)                                                                 |  |

| Converters (TTC) | 100ps                                  |                                                                                            |  |

| SATA-to-SMA      | Used to convert SATA interface         | Comax P/N H303000204A, or                                                                  |  |

| Test Fixture     | of PUT to SMA, for test                | Crescent Heart TF-SATA-NE-XP, or                                                           |  |

| CMA Tast Cold    | instrument connections                 | Agilent N5421-26401                                                                        |  |

| SMA Test Cables  | Used for all connections               | Agilent 15442-61601 (includes 4 cables) 8 total cables recommended.                        |  |

|                  |                                        | 8 total cables recommended.                                                                |  |

**Table A-1: Summary of Test Hardware Requirements**

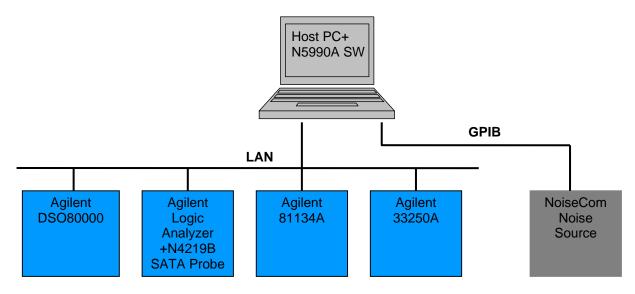

# A.2- Basic Test Setup

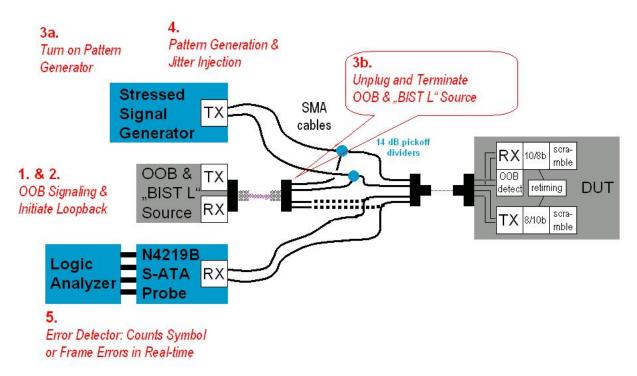

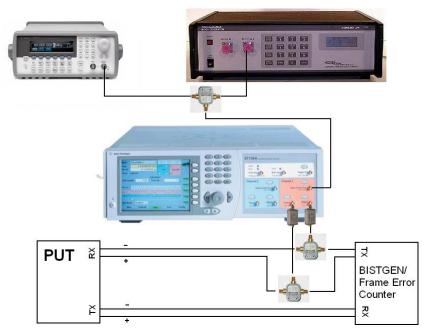

Figure A-1 shows a Test Setup that supports both disconnect and non-disconnect PUT's. The BIST Configuration Tool is multiplexed into the TX and RX pairs of the PUT using power splitters, which allow non-disconnect-supporting PUT's to be put into BIST-L using the BIST Configuration Tool, then be sent the framed COMP test pattern into their RX from the SSG while being monitored on the TX by the Frame Error Detector. Once the PUT is placed into BIST-L loopback mode, the BIST Configuration Tool can then be physically removed from the setup in order to run the formal test.

Figure A-1: Basic Test Configuration

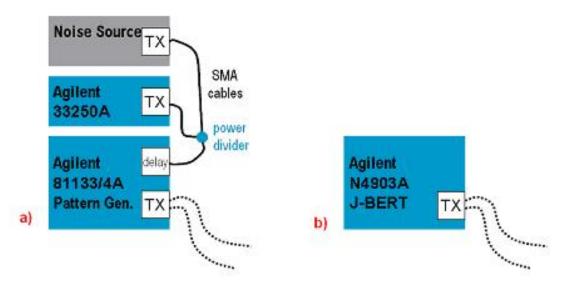

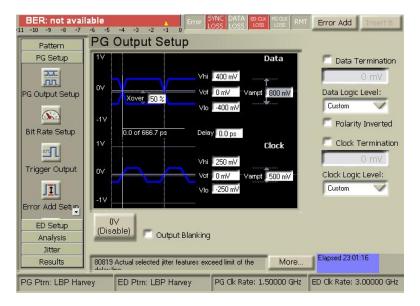

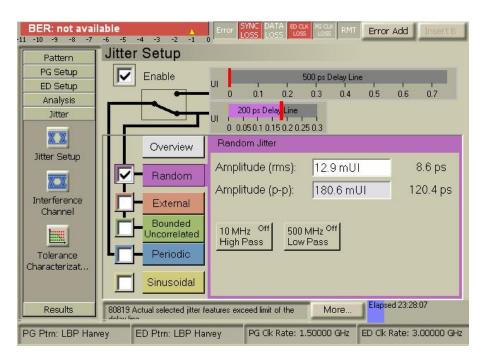

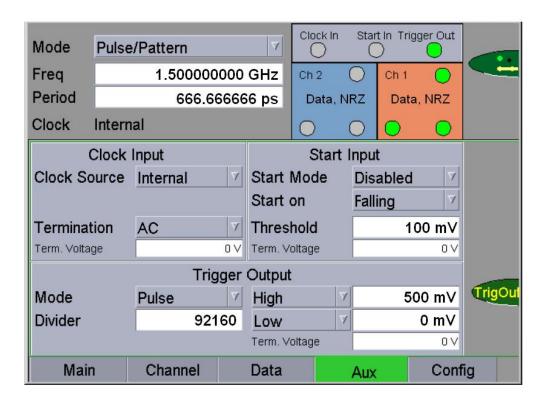

Figure A-2 illustrates how either the Agilent 81133A or 81134A pulse and pattern generator (a) or the Agilent N4903A J-BERT would be used as a SSG (b). If the J-BERT is used as the SSG, no external parts are required. The setup using the 81133/4A requires two external sources to generate jitter. The outputs of the Agilent 33250A Function/Arbitrary Waveform Generator and a gaussian Noise Generator are connected via a power divider to the 81133/4A's Delay Control Input.

Figure A-2: (a) Use of Agilent 81133A or 81134A as SSG, or (b) Agilent N4903A J-BERT (Gen2 only)

# A.3- Basic SSG Calibration Setup

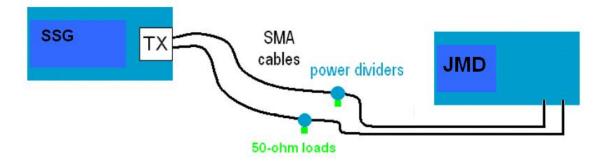

Figure A-3 shows the general block diagram setup for performing the Stressed Signal Generator (SSG) calibration procedure. The output of the SSG is sent through the power splitters (with the unused splitter ports terminated into 50 ohms) and the signal characteristics at the end of the SMA cables (the reference plane) are verified and adjusted using a Jitter Measurement Device to be at the necessary levels required for the RSG tests.

Figure A-3: Basic Calibration Setup

# Appendix B – SSG Calibration Procedure (using Agilent DSO81204 Real-Time DSO as the JMD)

**Purpose:** To define a procedure for verification and calibration of the stressed signal generator setup, using the Agilent Infiniium DSO81204 Real-Time DSO as the Jitter Measurement Device.

#### References:

[1] Serial ATA Interoperability Program Revision 1.2 Unified Test Document, Section 2.15

Last Modification: April 8, 2007

### **Discussion:**

Prior to running the actual stressed receiver tests, it is necessary to perform several steps to verify and calibrate the test system, in order to ensure that the signal delivered to the receiver of the PUT exhibits the proper type and amount of stress for the each test, as defined in [1].

First, we must verify that the SSG is providing the proper amounts of TJ and RJ at the reference plane. Note that the reference plane in this case is the end of the SMA cables, where they connect to the fixture that interfaces to the PUT.

The setup and calibration procedure is as follows:

# **B.1 - Configure the SSG to send the Framed COMP signal:**

• See Sections E.2 (for J-BERT) or F.2 (for 81134A) of this MOI.

### **B.2** - Calibrate the Differential Amplitude at the Reference Plane:

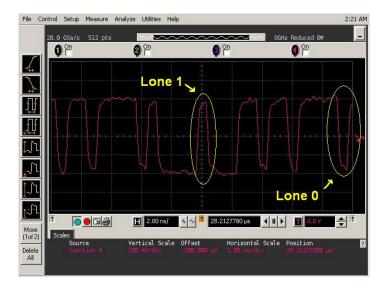

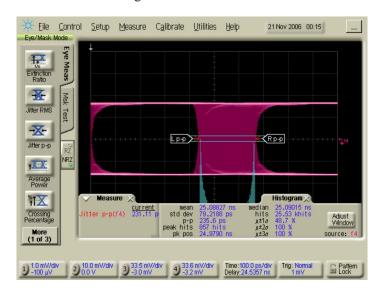

The amplitude calibration procedure requires measuring the amplitude of two particular bits contained in the framed COMP pattern, namely the Lone 0 and Lone 1 bits contained in the SATA Lone Bit Pattern (LBP). Performing this measurement requires isolating these bits on the scope so that the amplitude of only those bits can be measured. To do this, we will use a reference signal from the SSG, which is synchronized to the start of the Framed COMP pattern, as a trigger reference to trigger the scope. The delay can then be adjusted to isolate the desired bits, perform the amplitude measurement, and adjust accordingly.

This procedure assumes that the SSG possesses a trigger out signal, which can output a rising edge at the beginning of the pattern. (For details regarding particular SSG's, refer to Appendices E (J-BERT) and F (81134A) of this MOI.)

First, we will set up and connect the hardware:

- Connect the **Trigger Out** signal of the SSG to the **Channel 4 input** of the DSO.

- Using the diagram in **Appendix F, Figure F-1** as a guide, disconnect any SMA cables from the BISTGEN side of the splitters at the output of the SSG, and cap the splitter ports with 50-ohm SMA terminators.

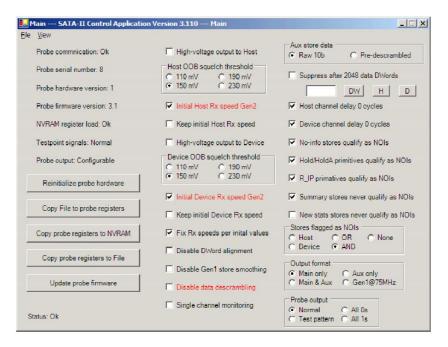

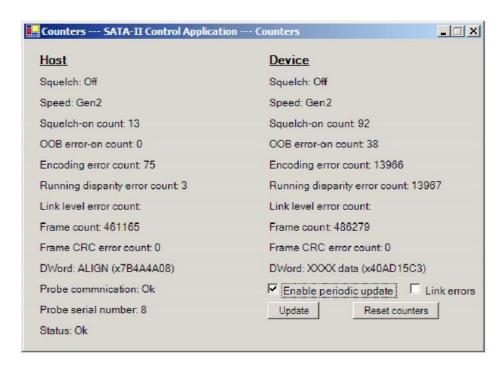

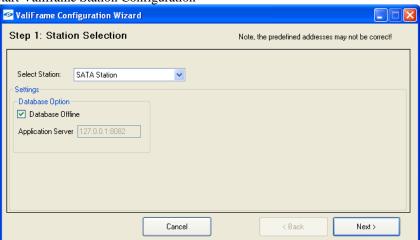

- On the PUT side of the splitters, leave the cables attached to the splitters, but disconnect them from the PUT, and put them into the DSO (+ into CH1, and into CH3).